# A Multiband, Low Power and Low Phase Noise CMOS Voltage-Controlled Oscillator with NMOS Varactor for UWB Applications

Hanen Saoudi, Hamadi Ghariani, Mongi Lahiani

Laboratory of Electronics and Technology of Information (LETI), National Engineers school of Sfax Electrical Engineers School Department. B.P.W, Sfax, TUNISIA 3038 hanen.saoudi@enis.tn

Abstract—A multiband low power and low phase noise LCtank Voltage Controlled Oscillator (VCO) is designed for low band channels of the standard IEEE 802.15.4a. The LC-VCO uses the structure of complementary cross-coupled differential negative resistance and tank circuit, which contains varactor arrays for frequency fine-tuning and a spiral inductor. A method that uses resistor tail biasing for reducing the phase noise and the power consumption has been adopted. The circuit is fully designed in TSMC's 180 nm technology process. The oscillator output provides three center frequencies of 3.5, 4, 4.5 GHz with good phase noises of -113.784, -116.703 and -126.753 dBc/MHZ at 1 MHz offset, while it dissipates 9mW power energy. The proposed LC VCO not only set a good balance between low phase noise and low power consumption, but it is also a highly desired circuit for multiband wireless transceiver systems, which are the major contributions of this proposed design.

$\label{eq:lower} \emph{Index Terms}{\----} LC~VCO; Phase~Noise; Multiband; Varactor; Low Power.$

## I. INTRODUCTION

With the wide variety of wireless communication technologies, multi-standard communication systems have received an increased interest among researchers. In this context, the Ultra-wideBand (UWB) technology has defined the IEEE 802.15.4a as a multi-standard, which splits the overall frequency band into UWB sub-band whose bandwidth is 528 MHz [1]. It allows designing transceivers with low power consumption, low complexity and high speed transmission by taking the benefits from the Impulse Radio (IR) technique [2].

This approach requires circuit designers to adopt a more compact and cost effective multiband oscillator, which is a key building block in any multiband transceiver used for carrier frequency synthesizes for up-convert and down-convert signal. To design multiband VCO, several methods have been developed, such as using switched differential inductor as proposed in [3] that generates multibands of 0.9, 1.8, 2.4 and 4.5 GHz. However, this technique increases the chip area and the power consumption due to the use of extra passive inductors.

Another way to achieve multiband LC VCO is to use switchable varactors and switchable capacitors block as reported in [4]. The proposed multiband VCO establishes a wide tuning range frequency from 4.5 to 6.5 GHz. with an average phase noise performance.

Recently, [5] proposes a wide tuning LC VCO using a tunable active inductor to generate an output frequency of 5.5GHz. Obviously, it is a compact VCO with easy integration; however, it has unsatisfactory phase noise of -81dBc/MHz.

In designing the LC VCO, the phase noise appears as the most challenging task because it reflects the quality and performance of information transfer. It is generally recognized that the major contributor to overall phase noise in LC VCO is the tail current source [6]. Thermal noise, which is added by the biasing circuit, is down converted and flicker noise is up converted during the mixing action resulting in increasing the phase noise. Thus, removing the tail biasing source seems as a solution to improve the phase noise criterion as reported in [7] although it considerably increases the power consumption in nominal conditions.

In turn, the strong combination of low power and low phase noise surges circuit designers to create a spectacular field of research toward the techniques used to enhance these metrics.

[8] uses the harmonics filter technique to filter out the second harmonic of the tail current noise. This approach incorporates a LC network in between switching transistors common node and tail current source. Hence, it allows the output noise to be reduced significantly to-130 dBc/Hz without increasing the power consumption. However, it presents the drawback of an increased chip area due to the use of additional inductors, and the lack of control circuit to widen the frequency tuning range.

Another approach based on using the tail current shaping method is demonstrated in [6]. It consists of current injection and two paths for current disconnection to reduce strongly the phase noise. This circuit proves as a good phase noise performance of-127 dBc/Hz from the carrier frequency of 1.65 GHz at the expense of increased circuit complexity and limited number of frequency bands.

Furthermore, [9] develops a novel biasing technique for LC VCO based on using a feedback loop and LD to generate an output current. This solution ensures the regulation of the bias current in order to eliminate the current source, as a consequence improving the phase noise performance. It works at around 2.25 GHz carrier frequency and achieves-127.2 dBc/Hz phase noise. However, this circuit suffers from increased complexity design and inability to generate various carrier frequencies.

Another alternative solution depicted in [10] consists of using a cross-coupled series LC resonator instead of using

parallel LC resonator. This technique generates a rectangular shaped voltage at the drain nodes of the switching pair. Thereby, it enhances the spectral purity output by amplifying the fundamental frequency and removing the noise and harmonics components. The proposed LC VCO enhances significantly the phase noise which is -126 dBc/Hz at 3.56 GHz carrier frequency without degrading the power consumption. The main drawback of the proposed method is that it is not able to provide several carrier frequencies.

Obviously, these structures meet the stringent requirements of low phase noise and low power consumption; however, they are not able to support a variety of wireless communication systems.

To overcome this bottleneck, the proposed LC VCO uses varactors bank in the tank to maximize both the tuning range and operating frequency. Moreover, it replaces the tail current source by a tail resistor biasing to reduce both phase noise and power consumption.

The resistor tail biasing serves as a source damping device to eliminate excess 1/f noise caused by the differential pair transistor when it is carefully chosen [11]. Furthermore, an adequate adjustment of this resistor can control the current consumption to avoid the oscillator from drawing current as much as it can.

This paper proposes the differential cross coupled LC VCO uses switched varactors banks structure and a resistor tail biasing to achieve a wide frequency tuning range, low phase noise and low power consumption. Following Section I, Section II presents the basic concepts about the proposed complementary cross-coupled LC oscillator topology and the C-V characteristics of an MOS varactor. In Section III, simulation results of the proposed circuit and comparison with other related works are presented. Finally, conclusions are drawn in Section V.

## II. CIRCUIT DESIGN

# A. Basic Concept

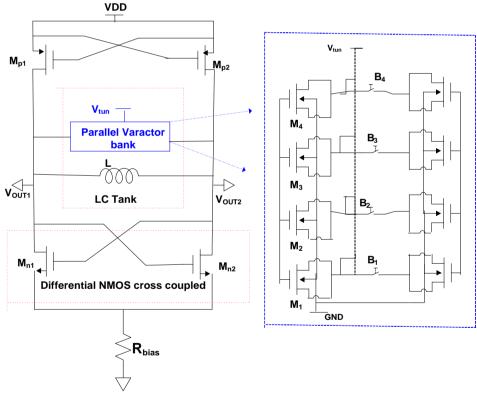

A complementary cross-coupled LC CMOS voltage controlled oscillator is shown in Figure 1. This structure is characterized by a good phase noise performance and easy start-up [12] condition by reducing the output signal amplitude. It is made up of active circuit, switched varactors block, passive inductor and tail resistor biasing. In this configuration, the active circuit consists of cross coupled pair NMOS and PMOS devices that are (Mn1, Mn2) and (Mp1, Mp2). This topology allows transistors to share the same bias current, which consequently leading to doubling the negative resistance for the same power consumption.

Figure 1: The circuit schematic of the proposed LC VCO

To guarantee that the circuit can enable sustained oscillation, the total negative resistance should be able to compensate the losses in the LC tank. The latest can be expressed as a parallel combination of the NMOS and PMOS pair's negative resistance,  $R_{in,n}$  and  $R_{in,p}$  as [13]:

$$R_{negative} = R_{in,n} / / R_{in,p} = -\frac{2}{G_{mn} + G_{mp}}$$

(1)

Taking account that these devices operate in the saturation region, the drain current will be given as below:

$$I_{dc} = \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right) \left(V_{gs} - V_{th}\right)^2 \tag{2}$$

Where  $\mu_n$ ,  $C_{ox}$ ,  $V_{gs}$  and  $V_{th}$  are the surface mobility of electron, the gate oxide capacitance, the gate to source voltage and the threshold voltage of NMOS transistor,

respectively. Thus, the transconductance of each transistor can be expressed as:

$$G_{m} = \frac{\partial I_{dc}}{\partial V_{gs}} | Q_{point} \rangle = C_{ox} \mu_{0} \left( \frac{W}{L} \right) (V_{gs} - V_{th})$$

(3)

In this proposed design, the tail current source is completely suppressed to improve the phase noise. Adding a tail biasing resistor at the common source point is used as an alternative solution to meet the issue of increased power consumption. This technique has great effect on enhancing the VCO performances.

First, the added resistor allows a flexible control of impedance at the common source to maintain the circuit working in current limited region, resulting in decreasing the overall power consumption.

Second, this technique eliminates extra noise generated by biasing circuit. Consequently, this technique provides great features for improving both phase noise and power consumption. As a result, this circuit can achieve lower power consumption and generates sufficient negative resistive to compensate the losses of LC tank core.

# B. Proposed Switched Varactor Bank

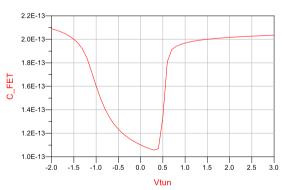

Integrated voltage controlled capacitance (varactor) is a key building block of the VCO used to generate the fine tuning frequency. PMOS varactors are widely used for linear devices like amplifiers. However, for nonlinear devices like mixers and oscillator, NMOS varactors are more desirable because they work faster due to their mobility of electrons, which is nearly two times more than the mobility of holes [14]. As a result, N- channel device has lower size and lower impedance of an equivalent P- channel device. Hence, NMOS varactor is selected in this work for a good start-up condition and high performance. By connecting the three terminals of MOS transistor drain, source and bulk (D, S, B) together, a variable capacitance appears depending on the voltage between bulk and gate. The characteristic C-V of NMOS varactor, which is formed with 67 gate fingers, each finger having a gate length of 0.18  $\mu$ m and a gate width of 1.5  $\mu$ m, is illustrated in Figure. 2.

Figure 2: Characteristic C-V of NMOS varactor

Thus, three major regions are displayed including accumulation, depletion and inversion.

Inversion mode is the best candidate due to its superior performance in terms of maximum capacitance value, phase noise characteristic and easy implantation, which is done by connecting together the remaining drain and source, while the bulk is connected to the ground. This proposed design includes multi-symmetrical bodybias varactors connected in parallel to increase the tenability of the proposed oscillator. The amount of capacitance is changed by varying the control voltage Vtun. To work under a precise frequency, the varactor block is digitally controlled by a binary array of autonomous control signals.

Hence, the resonance frequency of the tank is given as:

$$f_0 = \frac{1}{2\pi\sqrt{L_{\tan k}C_{\tan k}}} \tag{4}$$

where

$$L_{\tan k} = L$$

and  $C_{\tan k} = \frac{C_{\text{var}}}{2} + C_p = C_{\text{var}} + C_P$ ,

in which  $C_p$  and  $C_{\rm var}$  are the total parasitic capacitance and varactor capacitance.

Moreover, the tuning range (TR) criterion can be expressed as [4]:

$$TR = 2 \times \frac{f_{\text{max}} - f_{\text{min}}}{f_{\text{max}} - f_{\text{min}}} \%$$

(5)

where  $f_{\rm max}$  is the maximum oscillation frequency and  $f_{\rm min}$  is the minimum oscillation frequency.

By using (4) and (5), the tuning range is given by:

$$TR = 2 \times \frac{\left(\sqrt{C'_{\text{var,max}} + C_p}\right) - \left(\sqrt{C'_{\text{var,min}} + C_p}\right)}{\left(\sqrt{C'_{\text{var,max}} + C_p}\right) + \left(\sqrt{C'_{\text{var,min}} + C_p}\right)}$$

(6)

It is noted from equation (6) that the tuning range depends on the highest value and the lowest value of the MOS varactors. To determine accurately this great influence, TR expression can be simplified as:

$$TR = 2 \times \frac{\left(\sqrt{\frac{C_{\text{var,max}}^{'}}{C_{\text{var,min}}^{'}}} + \frac{C_{p}}{C_{\text{var,min}}^{'}}\right) - \left(\sqrt{1 + \frac{C_{p}}{C_{\text{var,min}}^{'}}}\right)}{\left(\sqrt{\frac{C_{\text{var,max}}^{'}}{C_{\text{var,min}}^{'}}} + \frac{C_{p}}{C_{\text{var,min}}^{'}}}\right) + \left(\sqrt{1 + \frac{C_{p}}{C_{\text{var,min}}^{'}}}\right)}$$

(7)

Hence, to maximize the tuning range it is demanded to increase the varator ratio  $C_{\rm var,max}^{'}$  /  $C_{\rm var,min}^{'}$  and reduce the parasitic capacitance  $C_{P}$ .

According to the above expression, we can conclude that the oscillation frequency is fixed by MOS varactors and inductor in LC resonator.

Table 1 shows the amount of transistors and values of passives elements.

Table 1 Values for Passive Elements and Transistor's Aspect Ratio

| Components                      | Specifications       |  |

|---------------------------------|----------------------|--|

| $M_1; (W/L)_1$                  | 30µm/0.18µm          |  |

| $M_2, M_3, M_4; (W/L)_{2,3,4}$  | $100\mu m/0.18\mu m$ |  |

| $M_{n1}, M_{n2}; (W/L)_{n1,n2}$ | $30\mu m/0.5\mu m$   |  |

| $M_{p1}, M_{p2}; (W/L)_{p1,p2}$ | 90μm/0.5μm           |  |

| $R_{bias}$                      | $200\Omega$          |  |

| L                               | 2 nH                 |  |

## III. SIMULATION RESULTS

The multiband low-phase-noise VCO has been implemented in  $0.18\mu m$  CMOS technology. The center frequencies are about 4.5, 4 and 3.5 GHz, which can be simulated with Advanced Design System (ADS) software by

using transient analysis, DC simulation, phase noise simulation and HB simulation.

To generate the three center frequencies, the inductance value is 2nH, and the total equivalent capacitance is in the range of 1.033pF to 0.625pF.

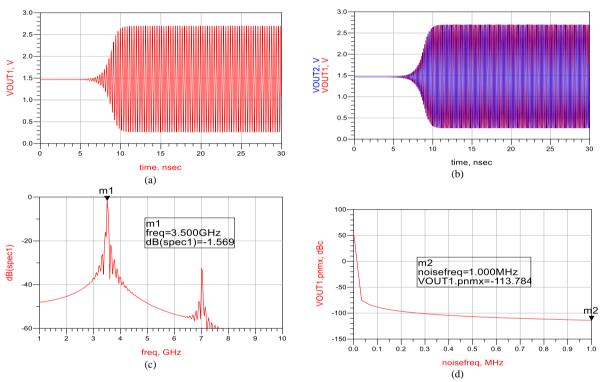

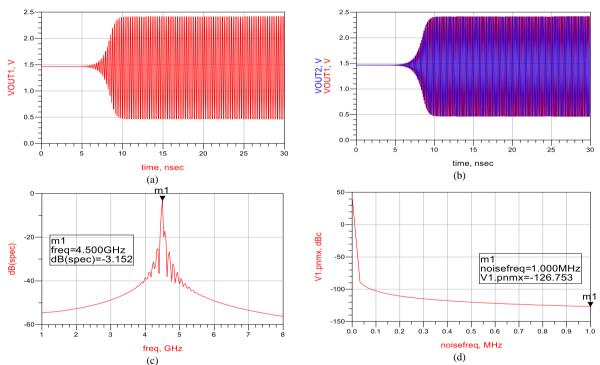

Figure 3 (a), (b), (c) and (d) show the simulated output waveform and its spectrum at frequency 3.5 GHz. It proves that the proposed circuit can enable sustained oscillation with an acceptable start-up time of 8ns.

For the lower frequency, it is needed to use the largest capacitance value; consequently, the four parallel varactors are used with an adequate control of Vtun voltage, which is fixed at 0.5V.

The amount of output power spectrum is -1.569 dBm and the phase noise is about -113.784 dBc/Hz at 1 MHz offset from carrier frequency  $f_{osc}$  of 3.5 GHz.

Figure 3: (a) Single ended transient response of VOUT1, (b) differential transient response, (c) phase noise response, (d) frequency spectrum of the LC-VCO at frequency 3.5 GHz.

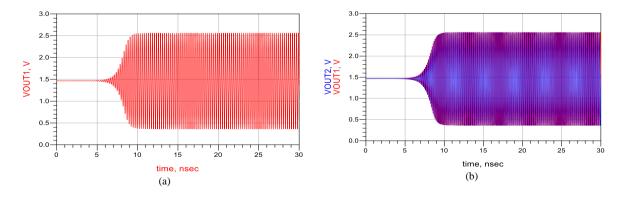

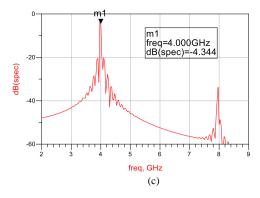

Figure 4: (a) Single ended transient response of VOUT1, (b) differential transient response, (c) phase noise response, (d) frequency spectrum of the LC-VCO at frequency 4 GHz.

As shown in Figure 4, the oscillations are able to sustain to guarantee the easy start up criterion at the center frequency of 4 GHz. To generate this desired frequency, only two NMOS varactors are used by setting the Vtun voltage of the last varactor at 1V. The amount of output power spectrum is -4.344 dBm and the phase noise is about -116.703 dBc/Hz at 1 MHz offset.

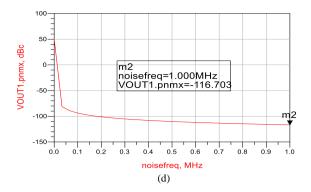

For the higher frequency of 4.5 GHz, it is demanded to use the smallest capacitance value. Hence, only one NMOS varactor is used with a settled Vtun at 2V. The amount of output power spectrum is -3.152 dBm and the phase noise is about -126.753 dBc/Hz at 1 MHz offset, as illustrated in Figure 5.

Notably, the phase noise increases as the number of varactors decreases and as the varactor gain decreases.

Figure 5: (a) Single ended transient response of VOUT1, (b) differential transient response, (c) phase noise response, (d) frequency spectrum of the LC-VCO at frequency 4.5 GHz.

The significant improvement in both phase noise and power consumption resulting from the resistor biasing has a sharp effect in enhancing Figure of Merit (FOM). This metric measures the VCO performance and is defined as [6]:

$$FOM = L\left\{f_{offset}\right\} - 20\log\left(\frac{f_c}{f_{offset}}\right) + 10\log\left(\frac{P_{DC}}{1mW}\right) (8)$$

where L {foffset}, PDC, are the phase noise at offset frequency (*foffset*) from the carrier frequency of *fc* and the DC power consumption of VCO in mW.

Table 2 summarizes the performance of the proposed LC VCO with recently published works. It shows good performances in terms of low power consumption, good phase noise and wide band tuning. Moreover, it fulfills the stringent requirement of miniaturization by reducing the number of circuit components.

Table 2

Performance Comparison of Multiband LC VCO

| Reference    | Technology (µm) | Frequency range (GHz)    | Phase noise at<br>1MHz offset<br>(dBc/Hz) | Power consumption (mW) | FOM<br>(dBc/Hz)              | YEAR         |

|--------------|-----------------|--------------------------|-------------------------------------------|------------------------|------------------------------|--------------|

| This work    | 0.18            | 3.5<br>4<br>4.5          | -113.784<br>-116.703<br>-126.753          | 9                      | -175.2<br>-179.2<br>-190.2   | 2018         |

| [3]          | 0.18            | 0.9<br>1.8<br>2.4<br>4.5 | -133<br>-135<br>-125<br>-127              | 16.2                   | -180<br>-188<br>-181<br>-188 | 2018         |

| [6]          | 0.18            | 1.65                     | -127.7                                    | 4.1                    | -186                         | 2018         |

| [9]          | 0.065           | 2.25                     | -127.2                                    | 5.6                    | -183.8                       | 2017         |

| [15]         | 0.18            | 0.9<br>1.8<br>2.4        | -104.7<br>-107.7<br>-101.7                | 5.3                    | -156.3<br>-164.5<br>-160.3   | 2017         |

| [16]<br>[10] | 0.18<br>0.065   | 10.6<br>3.56             | -107.779<br>-126                          | 9.8<br>5.6             |                              | 2017<br>2014 |

## VI. CONCLUSION

This paper presents a low power, low phase noise multiband LC VCO using a switched Varactor bank in a standard TSMC 0.18µm CMOS technology. The proposed LC VCO is achieved to operate at 3.5, 4, 4.5 GHz center frequencies. The phase noises are about -113.784 dBc/Hz, -116.703 dBc/Hz and -126.753 dBc/Hz at 1 MHz offset from carrier frequency fosc of 3.5GHz, 4 GHz and 4.5 GHz, respectively, while consuming 9mW of energy. Since the proposed LC VCO uses a switched varactors bank, which covers from 3 to 4.5 GHz, it can be used as a crucial block of multi-standard application. This work complies with the current debate to produce multifunction wireless device; hence, making the proposed LC VCO design as a challenging block for multiband and low power consumption wireless transceiver.

# REFERENCES

- [1] L. A. N. Man, S. Committee, "Part 15 . 4: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (WPANs)," IEEE Computer Society, vol. 2006, no. September. 2006, pp.2-305.

- [2] F. C. Commission, "Revision of Part 15 of the Commission's Rules Regarding Ultra-Wideband Transmission Systems," First Rep. Order ..., no. FCC02-48, pp. 1–118, 2002.

- [3] J. Kim, J. Park, and J. Kim, "A low phase noise multi-band LC VCO using a switched di ff erential inductor," *IEICE Electronics Express*, vol. 15, no. 7, pp. 1–7, 2018.

- [4] X. Lei, J. Zhang, and J. Shi, "Analysis and Design of a Wideband Low Phase Noise LC VCO," *PIERS Proceedings*, vol. 2, no. 2, pp. 968–972, 2015.

- [5] N. C. Shirazi and R. Hamzehyan, "Design of VCO with a Differential

- Tunable Active Inductor," Int. J. of Machine learning and computer, vol. 3, no. 1, pp. 3–6, 2013.

- [6] B. Jafari and S. Sheikhaei, "Pseudo-impulse tail current shaping for phase noise reduction in CMOS LC oscillators," *Microelectronics J.*, vol. 74, no. December 2017, pp. 60–68, 2018.

- vol. 74, no. December 2017, pp. 60–68, 2018.

[7] A. Hajimiri and T. H. Lee, "Design Issues in CMOS Differential LC Oscillators," *IEEE J. of solid state circuit*, vol. 34, no. 5, pp. 717–724, 1999

- [8] B. Jafari and S. Sheikhaei, "Phase noise reduction in a CMOS LC cross coupled oscillator using a novel tail current noise second harmonic fi Itering technique," *Microelectronics J.*, vol. 65, no. May, pp. 21–30, 2017.

- [9] I. F. I. Albittar, H. Dogan, and M. T. Ozgun, "A novel biasing technique for low phase noise voltage controlled oscillators," *Microelectronics J.*, vol. 72, no. May 2017, pp. 120–125, 2018.

- [10] N. Oh, "A phase-noise reduction technique for RF CMOS voltagecontrolled oscillator with a series LC resonator," *Microelectronics J.*, vol. 45, pp. 435–440, 2014.

- [11] S. D. Resistors, "RF CMOS LC -Oscillator With Source Damping Resistors," *IEEE Microwave and Wirelles Components letters*, vol. 16, no. 9, pp. 511–513, 2006.

- [12] Y.J. Moon, Y.S. Roh, C.Y. J, and C. Y, "A 4.39–5.26 GHz LC-Tank CMOS Voltage-Controlled Oscillator With Small VCO-Gain Variation," *IEEE Microwave and Wireless Components Letters*, vol. 19, no. 8, pp. 524–526, 2009.

- [13] A. Nasri and M. Yargholi, "Design of a LC-Tank CMOS Voltage-Controlled Oscillator," Int. J.of Research in Electrical and Electronics technology, vol. 1, no. 2, pp. 33–37, 2014.

- [14] A. L. Phase and N. Lc-vco, "A 4GHz Low Phase Noise LC-VCO in 0.18μm CMOS Technology," Int. Conf on Power Electronics, Systems and Applications, pp. 18–21, 2012.

- [15] V. Narayana and R. Vanukuru, "A High Performance Switchable Multiband Inductor Structure for LC-VCOs," *Int. Conf. on VLSI Design*, pp. 253–258, 2017.

- [16] H. Saoudi, M. Dhieb, H. Ghariani, and M. Lahiani, "Design of 10.6 GHZ low phase noise LC-Voltage controlled oscillator in 0.18 3 m CMOS Technology," Int. Conf On Sciences and Techniques of Automatic control & Computer engineering, pp. 1–7, 2017.