# An FPGA Approach for EXP-BET Metrics Computation Using Simulink Blockset

Y. Yusuf<sup>1</sup>, D. M. Ali<sup>1</sup>, A. A. A. Rahman<sup>2</sup> and A. K. Samingan<sup>2</sup>

<sup>1</sup>Wireless Communication Technology Group (WiCoT),

Advanced Computing and Communication Communities of Research, Faculty of Electrical Engineering,

Universiti Teknologi Mara (UiTM), 40450 Shah Alam, Selangor Darul Ehsan, Malaysia.

<sup>2</sup>*TM Research & Development Sdn. Bhd, TM Innovation Centre,*

Lingkaran Teknokrat Timur, 63000 Cyberjaya, Selangor Malaysia.

ymardiahyusuf@gmail.com

Abstract—This paper proposes the process of simulating the mathematical model of the EXP-BET scheduling algorithm using MATLAB Simulink configured with Xilinx System Generator (XSG). The system generator provides Simulink blockset for several hardware operations that could be implemented on various Xilinx FPGAs. The method describes in this paper involves the calculation of metrics equation for EXP-BET scheduling algorithm and the model is developed using constant values for all the parameters in the equations. Many applications that are DSP based require mathematical modeling for easy understanding and analysis. Furthermore, the need of instant prototyping tools such as MATLAB Simulink and Xilinx System Generator has become increasingly important because of the limitation for time-to-market. This can greatly reduce the process cycle from the algorithm to the hardware implementation. The output of the simulation demonstrated that EXP-BET metrics computation was successfully the accomplished.

*Index Terms*—EXP-BET Scheduling Algorithm; MATLAB Simulink; System Generator.

## I. INTRODUCTION

Matrix Laboratory namely as MATLAB is a numerical computing environment and modern (fourth generation) programming language developed by Math Works. MATLAB integrates computation, visualization, and programming environment that allow matrix manipulations, plotting of functions and data, implementation of algorithms, creation of graphic user interface (GUI) and interfacing with programs [1]. Simulink is an additional package in MATLAB provide platform for Model-Based design besides a good tool to test signals and visualize outputs during simulation.

Model-Based Design is a process that enables faster, more cost-effective development of dynamic systems, including control systems, signal processing and communications systems [2]. The method of Model-Based Design is significantly different from the procedure in the traditional design. The designers can formulate advanced functional characteristics by using continuous-time and discrete-time computational building blocks rather than using complex structures and extensive software code [2].

This paper presents the simulation of the Exponential Blind Equal Throughput (EXP-BET) scheduling algorithm's metrics equation using MATLAB Simulink configured with Xilinx System Generator (XSG). Scheduling mechanism is the process of dynamically allocating radio resources to User Equipment (UE) that transmits different flows at the same time. The significance of radio resource management algorithms are to elevate the performance of the end user and system capacity in Long Term Evolution Standard (LTE) Network.

Since the implementation of scheduling algorithm is not standardized in LTE, thus the network vendors can design and tune the algorithms according to the needs [3]. Previously, various scheduling algorithm which offered several techniques in handling resources to the users have been developed such as Modified Largest Weight Delay First (MLWDF), Proportional Fairness (PF), and Maximum Rate [4].

In 2016, K. S. Syahidah et al. [5] published a paper which described the performance of the EXP-BET scheduling algorithm towards the Frame Level Scheduler (FLS) [6] and Exponential Proportional Fairness (EXP-PF). The authors summarized that the EXP-BET outperformed the EXP-PF and FLS algorithms for the real time services such as video gaming and video streaming and the non-real time service which includes web browsing and email. EXP-BET has shown 17.72% improvement than FLS and 7.52% for EXP-PF in terms of fairness index.

To the best of our knowledge, none of the researchers have implemented the EXP-BET algorithm for the FPGA implementation using MATLAB Simulink. In a different study conducted by Liyana et al. [7], they have primarily concentrated on the implementation of FPGA for various algorithms used in arbiters. At present, FPGAs have large resources of Look up tables (LUTs) logic gates and RAM blocks to support any complex digital computations. FPGA is called as the field programmable gate array because the FPGA board itself can be configured or programmed by the user. The programming language of the FPGA is coded using Hardware Description Language (HDL) such as Verilog HDL and VHDL.

The researchers in paper [8] proposed a methodology for simulation process of a complex mathematical model. The authors simulated the mathematical model of Differential Phase Shift Keying (DPSK) and Fast Fourier Transform (FFT) using Xilinx System Generator and MATLAB Simulink environments. Due to the complexity of the mathematical algorithm, the authors concluded that the mathematical modeling for DPSK and FFT cannot be simulated using pure HDL code besides; it is costly and time consuming.

Another studies by Mohamed Ali Hajjaji [9] proposed a real time implementation system of numerical watermarking

system using MATLAB Simulink and Xilinx System Generator (XSG). The methodology used follows the hardware implementation on the FPGA Xilinx. The authors reported that the hardware system gives good results which is similar to those obtained using the simulation of the MATLAB Simulink.

The main contribution of this work is to develop the method used to implement the algorithm in LTE Networks. The development of wireless networks is a long term procedure that comprise of many stages. At some point, simulation on a hardware is required to validate the theoretical work. The corresponding hardware implementation are used not only for theory verification, but there are also some concepts that should be seriously studied in practice. Hence, hardware platforms is vital in verifying these advantages in real environment.

Therefore, this study aims to demonstrate and investigate the simulation of EXP-BET algorithm using MATLAB Simulink and XSG. The proposed algorithm is the combination of EXP and BET equations. The algorithm is modelled using MATLAB Simulink configured with System Generator. The paper is organized as follow: in Section II, we describe the proposed algorithm's metrics equation. Section III presents the experimental model using MATLAB Simulink blockset and results. Finally section IV draws the conclusion and future work.

## II. SCHEDULING ALGORITHMS IN LTE NETWORKS

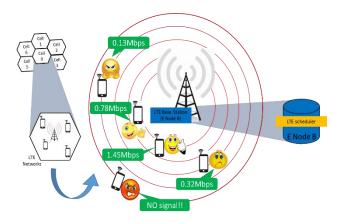

A base station is a fixed communication location and it is part of a network's wireless telephone system. It receives and passes on information to and from a communication device such as a mobile phone. A base station allows mobile phones to work within a local area or a cell site as illustrated in Figure 1.

Figure 1: Single cell environment

LTE base station, known as Evolved Node B (E-Node B) which is used to operate all radio resource management (RRM) functions. Packet scheduling is one of the RRM function. Scheduling mechanism is the process of dynamically allocating radio resources (time and frequency) to User Equipment (UE) that transmitting different flows at the same time. In downlink scheduler, the selection is done based on CQI report from the UE, channel quality and Quality of Service (QoS) requirements from radio bearers.

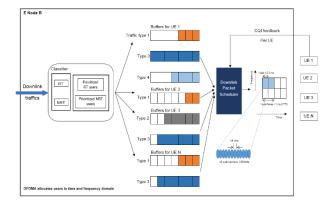

Figure 2: General downlink packet scheduling algorithm [10]

A buffer is given to each user in a cell at e-Node B as shown in Figure 2. Packets arriving into the buffer are time stamped and queued for transmission according to the first in first out (FIFO) principle. The packet scheduler decides which user is to be scheduled based on the packet scheduling algorithm in each time transmission interval (TTI). During each TTI, the scheduler shall consider the physical radio environment per UE. The UEs report their perceived radio quality (CQI report), as an input to the scheduler to decide which Modulation and Coding scheme (MCS) to use. The reported channel quality indicator (CQI) is a number indicating the most efficient MCS. In addition to the CQI value(s) reported by UEs, the e-Node B can use other information, such as Hybrid automatic repeat request (HARQ) retransmissions, to decide and request the link adaptation and selected MCS.

When a user moves far away from base station, the signal will degraded as compared to the signal near the base station. This will lead to unfair treatment to the user at the edge of the cell which means that they tend to get bad internet connection as illustrated in figure 1. The EXP-BET packet scheduler is developed to give an equal treatment to users regardless of where they are located in a cell. It means that, the user that experiencing the lowest signal will be served and they will get the same treatment as the user near the base station. The EXP-BET is the packet scheduler served the users based on the metrics equation.

## A. Exponential Rule Algorithm

EXP rule gives higher priority to UE which has more packets in its buffer or UE with highest transmission delay [10]. User with the highest priority metrics is allocated the resources firstly which is calculated using the equation of the EXP Rule algorithm. EXP rule is a channel-aware scheduling algorithm and is proven to be the most promising approach for delay-sensitive real-time applications such as video and VoIP. The priority metrics equation for EXP Rule [11] that mathematically describes the algorithm is:

$$m_{i,k}^{EXP \ Rule} = exp\left(\frac{a_i D_{HoL,i}}{1 + \sqrt{AverageD_{HoL}}}\right) * \Gamma_k^i \tag{1}$$

where:

$\alpha_i \qquad : \text{Tunable parameter, equal to } \frac{5}{0.99\tau_i}$  $\tau_i \qquad : \text{Maximum allowable delay}$  $D_{Hal} \qquad : \text{Delay of the first packet to be transmitted}$  by the  $i^{th}$  user

$$Average D_{HoL} : \frac{1}{N_{RT}} \sum_{i=1}^{N_{RT}} D_{HoL}$$

$$N_{RT} : \text{Number of active downlink real time flows}$$

$$\Gamma_k^i : \text{Spectral efficiency for } i^{\text{th}} \text{ user over}$$

# resource block

# B. Blind Equal Throughput

Accordingly, the BET algorithm [11] provides throughput fairness among all active users irrespective of the user location. The user will be allocated based on the metrics formula:

$$m_{i,k}^{BET} = \frac{1}{R_i(t)} \tag{2}$$

$k^{\text{th}}$

where:

$\begin{array}{ll} R_i(t) & : \beta R_i(t-1) + (1-\beta)r_i(t) \\ B & : \text{Weight factor} \\ R_i(t-1) & : \text{Past average throughput of the user at time } t-1 \\ r_i(t) & : \text{Achievable data rate for user } i^{\text{th}} \text{ at time } t^{\text{th}} \end{array}$

## III. EXP-BET MODELING

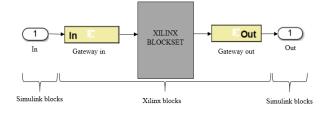

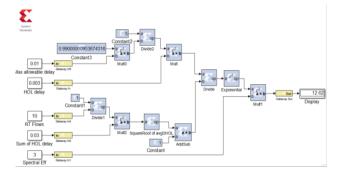

In the Simulink environment, the FPGA frontier is defined in the Gateway In and Gateway Out blocks. The input and output from the FPGA is fed into the Gateway In and the output is produced from the Gateway Out port. In the Gateway In block, the Simulink floating point input is converted to a fixed point format, saturation and rounding modes. The model of the system generator is as illustrated in Figure 3. These ports interface the Simulink double data type and the FPGA fixed point environments.

Figure 3: The model of the system generator used in the Simulink

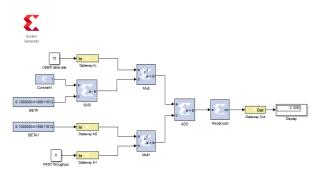

Figure 4: The Simulink model for the BET metrics equation

Figure 5: The Simulink model for EXP Rule metrics equation

The metrics equation for EXP and BET using Xilinx Blockset is created using Simulink Blockset. The system is tested by deploying a constant input to the system and the result is displayed on a Simulink's display block. The library used in Simulink environment for both mathematical equation are from the library of Sink, Sources and Xilinx Blockset.

# IV. RESULT AND DISCUSSION

The Simulink is used to verify the functionality of the model after the system is modelled. The testing process for the system is done by giving a constant input to the system so that the output will display a single value. System generator starts to process each block in the model and generate a simulation model according to the specific configuration of each block as depicted in Figures 4 and 5.

Table 1 EXP-BET Parameter Values

| Algorithms                | Parameter                 | Value |

|---------------------------|---------------------------|-------|

| Exponential Rule          | maximum allowable delay   | 0.01  |

|                           | head of line delay        | 0.003 |

|                           | sum of Head of line delay | 0.03  |

|                           | Real-time flows           | 10    |

|                           | spectral efficiency       | 3     |

| Blind Equal<br>Throughput | beta                      | 0.1   |

|                           | User throughput           | 10    |

|                           | Past average throughput   | 5     |

Table 1 presents the values used for Equations (1) and (2) during the simulation process. Hence, by referring to equation 1 and 2, the expected output of the EXP Rule system should be 12.62 whereas the output of the BET calculation should be 0.1053 respectively. The system for BET is quite simple since it only involves basic mathematical operations such as addition, subtraction, multiplication and division operations. The system can be verified by inspecting the output of the model as can be seen in Figures 4 and 5 generated by System Generator and Simulink.

#### V. CONCLUSION

MATLAB Simulink is the platform that provides simple and easy to use tool for developing mathematical computing based algorithm. In terms of hardware implementation to FPGA, the configuration of System Generator with MATLAB Simulink is more suitable and beneficial option compared translated the algorithms using VHDL or Verilog HDL. The EXP-BET is an algorithm which consists of the Exponential Rule (EXP Rule) and Blind Equal Throughput (BET). The work presented was designed and simulated using the Xilinx System Generator and MATLAB Simulink environment. This resulted in a mathematical modeling of the EXP-BET metric equation using System Generator blocks, simulation and modification of these blocks.

Thus, future research should concentrate on the hardware verification for EXP-BET algorithm into FPGA platform by following the Xilinx System Generator design methodology named hardware co-simulation method.

# ACKNOWLEDGMENT

This research was supported by Universiti Teknologi MARA (UiTM) and Kementerian Sains, Teknologi dan Inovasi (MOSTI).

#### REFERENCES

- [1] MathWorks, Inc., "What is model-based design?" available online at http://www.mathworks.com/model-based-design/.

- [2] Tatiana Kelemenova, Michal Kelemen, Lubica Mikova, Vladislav Maxim, Erik Prada, Tomas Liptak, Frantisek Menda, "Model based design and HIL simulations", American Journal of Mechanical Engineering, Vol. 1, No. 7, 276-281, 2013.

- [3] Samia Dardouri, Ridha Bouallegue, "comparative study of scheduling algorithms for LTE networks, International Journal of Computer, Electrical, Automation, Control and Information Engineering", Vol. 8, No. 3, 2014.

- [4] Chiapin Wang, Yi-Pu Chung, Kuo-Chang Ting, Chih-Cheng Tseng, Hwang-Cheng Wang, Fang-Chang Kuo, "Hybrid maximum-rate and proportional-fairness resource allocation in the downlink of LTE networks", IEEE, 2014.

- [5] Ku Siti Syahidah Ku Mohd Noh, Darmawaty Mohd Ali, Zin Mar Myo, Ahmad Kamsani Samingan, Abdul Aziz Abdul Rahman, Norsuzila Ya'acob, "Performance analysis of EXP-BET algorithm for triple play services in LTE system", Jurnal Teknolog, 13-18, 2016.

- [6] Mustafa Ismael Salman, Chee Kyun Ng, Nor Kamariah Noordin, Borhanuddin Mohd Ali and Aduwati Sali, "CQI-MCS mapping for green LTE downlink transmission", Proceedings of the Asia-Pacific Advanced Network 2013 Vol. 36, pp. 74-82, 2013.

- [7] Liyana Nazir, Roohie Naaz Mir, "Performance analysis of various scheduling algorithms using FPGA platforms", International Conference on VLSI Systems, Architecture, Technology and Applications, 2015.

- [8] Miss Shruti R. Tambakhe, Prof Ajay P. Thakare, "Design and simulation of mathematical models using mixed HDL platform", International Journal of Application of Innovation in Engineering & Management (IJAIEM), Vol. 3, No. 3, 2014.

- [9] Mohamed Ali Hajjaji, Abdessalem Ben Abdellali, Nada Farhani, Mohamed Gafsi and Abdellatif Mtibaa, "Real time implementation of numerical watermarking system using XSG", 16th International Conference on Sciences and Techniques of Automatic Control & Computer Engineering, 21-23, 2015.

- [10] Ku Siti Syahidah Ku Mohd Noh, Darmawaty Mohd Ali, Abdul Aziz Abdul Rahman, Ahmad Kamsani Samingan, Yusmardiah Yusuf, Nurulanis Mohd Yusuff, "Performance analysis of EXP-BET algorithm", Jurnal Teknologi, APPEMSE, accepted and presented January 2016.

- [11] Giuseppe. Piro, F. Capozzi, IEEE members, "Downlink packet scheduling in LTE cellular networks: key and design issues", IEEE Communications Surveys & Tutorials, Vol. 15, No. 2, 2013.

- [12] Bilal Sadiq, Ritesh Madan and Ashwin Sampath, "Downlink scheduling for multi-class traffic in LTE", EURASIP Journal on Wireless Communications and Networking, 2009.